锁相环及其应用

[TOC]

1.基本原理

- 锁相环(phase-locked loop,PLL)是一个能够比较输出与输入相位差的反馈系统,利用外部输入的参考信号控制环路内部振荡信号的频率和相位,使振荡信号同步至参考信号。

- PLL最早由法国工程师Henri de Bellescize在1932年提出。

- 基本结构与信号:

其中PD为鉴相器,LPF为环路滤波器(低通滤波器),VCO为压控振荡器。

$V_{in}$为外部输入的参考信号,$V_{out}$为输出信号,两者存在相位差,经过PD后输出一个差值信号$V_{PD}$,$V_{PD}$中包含高频分量和低频分量,也就是说$V_{PD}$是一个变化的信号,只有通过LPF处理后变为稳定的低频电压信号$V_{cont}$才可以驱动控制VCO,$V_{cont}$不断控制VCO调整内部振荡频率,最终使$V_{in}$和$V_{out}$的频率与相位达到同步状态。

2.主要应用

- 频率合成器

其中$÷M$、$÷N$模块为分频器,分别称为“M分频”和“N分频”。

经过上述两个分频器处理,PLL中进入鉴相器的信号有如下关系:

$$

\frac{f_{ref} }{M} = \frac{f_{out} }{N} \Rightarrow f_{out} = \frac{N}{M} f_{ref}

$$

通过调节M、N可以实现对输出频率的灵活控制,而且输出信号的频率稳定性与输入信号的频率稳定性是一致的。

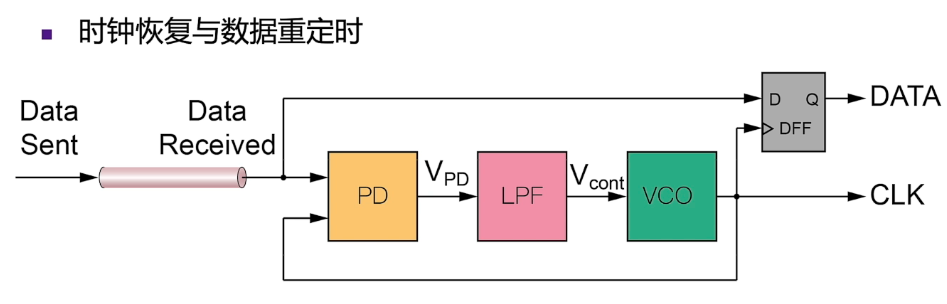

- 时钟恢复与数据重定时

将接收信号作为参考信号,最终经过PLL的输出信号是一个时钟信号CLK,该时钟是与接收信号同步上的时钟信号,即实现了信号的时钟恢复。

通过接收数据与时钟数据通过采样电路再对接收数据进行一次采样,将接收数据重新定位到时钟CLK上,最终得到重定时的数据DATA。

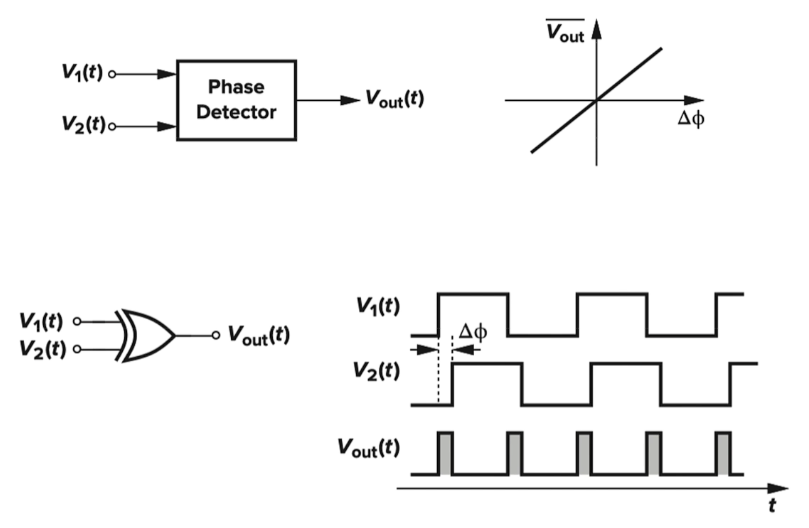

3.鉴相器(phase detector,PD)

理想的鉴相器输入输出特性曲线应该如下图所示,输入相位差$\Delta \varphi $应该和输出电压$V_{out}$是线性关系。

最简单的实现方式是:异或门。

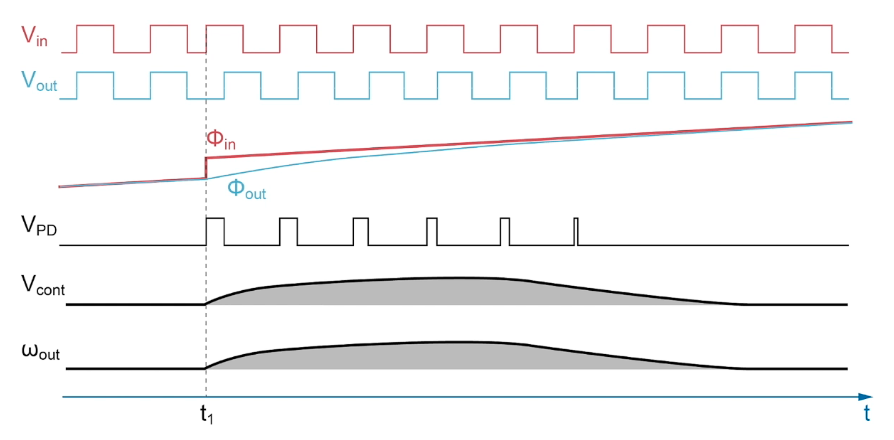

4.PLL对相位阶跃的响应

5.参考文献

https://www.bilibili.com/video/BV1fb4y1H7gv

22-3-24

http://example.com/2022/03/24/锁相环及其应用22-3-24/